# Intermediate Representations

Copyright 2010, Keith D. Cooper & Linda Torczon, all rights reserved. Faculty from other educational institutions may use these materials for nonprofit educational purposes, provided this copyright notice is preserved.

### Where In The Course Are We?

- We are on the cusp of the art, science, & engineering of compilation

- Scanning & parsing are applications of automata theory

- Context-sensitive analysis, as covered in class, is mostly software engineering

- The mid-section of the course will focus on issues where the compiler writer needs to choose among alternatives

- The choices matter; they affect the quality of compiled code

- There may be no "best answer" or "best practice"

The fun begins at this point

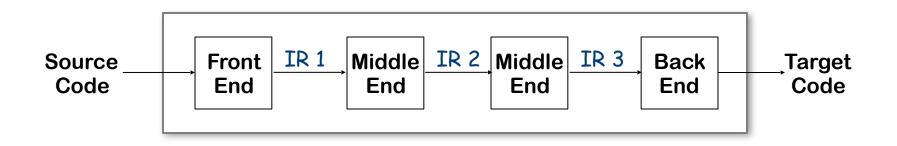

### Intermediate Representations

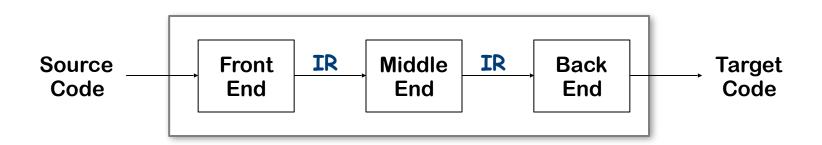

- Front end produces an intermediate representation (IR)

- Middle end transforms the IR into an equivalent IR that runs more efficiently

- Back end transforms the IR into native code

- IR encodes the compiler's knowledge of the program

- Middle end usually consists of several passes

### Intermediate Representations

- Decisions in IR design affect the speed and efficiency of the compiler

- Some important IR properties

- Ease of generation

- Ease of manipulation

- The importance of different properties varies between compilers

- Selecting an appropriate IR for a compiler is critical

- Three axes of choice: structural organisation, level of abstraction, naming discipline

# Structural organisation

Three major categories

- Structural

- Graphically oriented

- Heavily used in source-to-source translators

- Tend to be large

- Linear

- Pseudo-code for an abstract machine

- Level of abstraction varies

- Simple, compact data structures

- Easier to rearrange

- Hybrid

- Combination of graphs and linear code

Examples: Trees, DAGs

Examples: 3 address code Stack machine code

Example: Control-flow graph

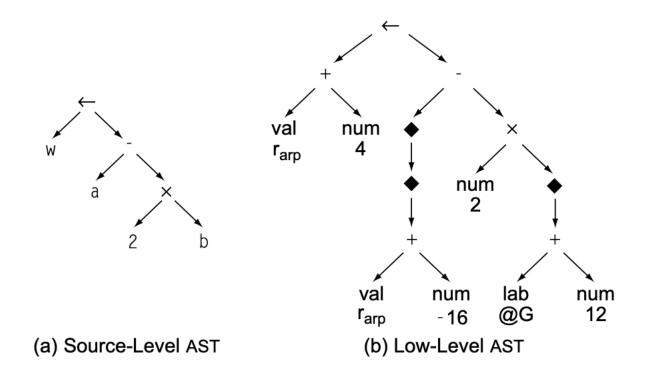

### AST with different level of abstraction

### Level of Abstraction

- The level of detail exposed in an IR influences the profitability and feasibility of different optimizations.

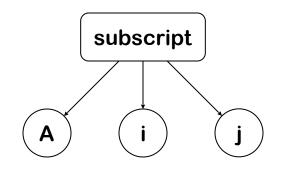

- Two different representations of an array reference:

array A[1...10,1...10] of 1 byte memorised in row-major order

High level AST: Good for memory disambiguation

| loadI                         | 1                |                | => | $r_1$          |

|-------------------------------|------------------|----------------|----|----------------|

| sub                           | r <sub>j</sub> , | $r_1$          | => | r <sub>2</sub> |

| loadI                         | 10               |                | => | r <sub>3</sub> |

| mult                          | $r_2$ ,          | r <sub>3</sub> | => | $r_4$          |

| sub                           | r <sub>i</sub> , | $r_1$          | => | r <sub>5</sub> |

| add                           | $r_4$ ,          | $r_5$          | => | r <sub>6</sub> |

| loadI                         | @A               |                | => | r <sub>7</sub> |

| add                           | $r_{7}$ ,        | r <sub>6</sub> | => | r <sub>8</sub> |

| load                          | r <sub>8</sub>   |                | => | $r_{Aij}$      |

| Low level linear code:        |                  |                |    |                |

| Good for further optimisation |                  |                |    |                |

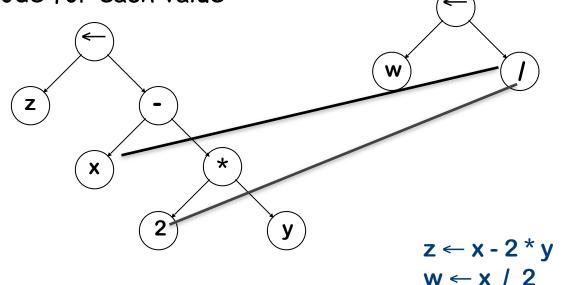

Directed Acyclic Graph

A directed acyclic graph (DAG) is an AST with a unique node for each value

- Makes sharing explicit

- Encodes redundancy

With two copies of the same expression, the compiler might be able to arrange the code to evaluate it only once. The third axis : naming

• The compiler must choose names for a variety of distinct values.

• a-2\*b

+1<-b</li>

+2<-2\*+1</li>

+3<-a</li>

+4<-+3-+2</li>

+1,+2,+3 and +4 are new names

If every subexpression has a name the compiler can reuse the value of the subexpression

# Naming : Stack Machine Code

Originally used for stack-based computers, now Java

| • | Example:  |         | push x           |

|---|-----------|---------|------------------|

|   | x - 2 * y | becomes | push 2<br>push y |

|   |           |         | multiply         |

|   |           |         | subtract         |

Advantages

- Compact form

- Introduced names are implicit, not explicit

- Simple to generate and execute code

Useful where code is transmitted over slow communication links (the net)

Implicit names take up no space, where explicit ones do!

### Three Address Code

Several different representations of three address code

• In general, three address code has statements of the form:

With 1 operator ( $\underline{op}$ ) and, at most, 3 names (x, y, & z)

Advantages:

- Resembles many real machines

- Introduces a new set of names

- Compact form

### Three Address Code: Quadruples

#### Naïve representation of three address code

- Table of k \* 4 small integers

- Simple record structure

- Easy to reorder

- Explicit names

| load  | r1, | У   |    |

|-------|-----|-----|----|

| loadI | r2, | 2   |    |

| mult  | r3, | r2, | r1 |

| load  | r4, | Х   |    |

| sub   | r5, | r4, | r3 |

The original FORTRAN compiler used "quads"

| load  | 1 | У |   |

|-------|---|---|---|

| loadi | 2 | 2 |   |

| mult  | 3 | 2 | 1 |

| load  | 4 | x |   |

| sub   | 5 | 4 | 3 |

RISC assembly code

Quadruples

### Three Address Code: Triples

- Index used as implicit name

- 25% less space consumed than quads

- Much harder to reorder

| (1) | load  | У   |     |

|-----|-------|-----|-----|

| (2) | loadI | 2   |     |

| (3) | mult  | (1) | (2) |

| (4) | load  | x   |     |

| (5) | sub   | (4) | (3) |

| load  | r1, | У   |    |

|-------|-----|-----|----|

| loadI | r2, | 2   |    |

| mult  | r3, | r2, | r1 |

| load  | r4, | Х   |    |

| sub   | r5, | r4, | r3 |

Implicit names occupy no space

Remember, for a long time, 640Kb was a lot of RAM

- Major tradeoff between quads and triples is compactness versus ease of manipulation

- -In the past compile-time space was critical

- -Today, speed may be more important

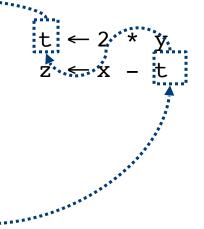

### Two Address Code

Allows statements of the form

$x \leftarrow x \text{ op } y$ Has 1 operator (op) and, at most, 2 names (x and y)

Example: $t_1 \leftarrow 2$  $z \leftarrow x - 2 * y$ becomes $t_2 \leftarrow 1$ oad y $t_2 \leftarrow t_2 * t_1$ • Can be very compact $z \leftarrow 1$ oad x $z \leftarrow z - t_2$

Problems

- Machines no longer rely on destructive operations

- Difficult name space

- Destructive operations make reuse hard

- Good model for machines with destructive ops (PDP-11)

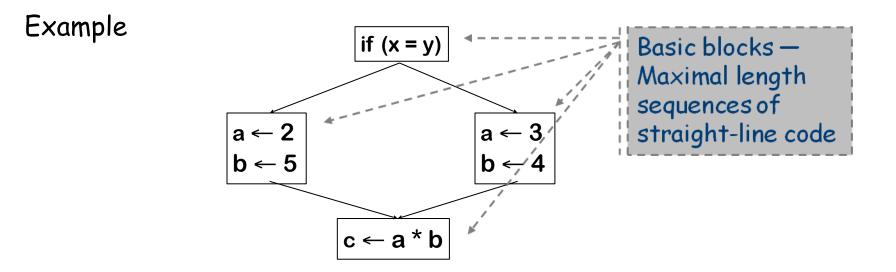

# Control-flow Graph

Models the transfer of control in the procedure

- Nodes in the graph are basic blocks

- Can be represented with quads or any other linear representation

- Edges in the graph represent control flow

# Static Single Assignment Form

- The main idea: each name is defined exactly once

- The name refers to the variable in some program point

- Encodes both control and value flow

Original

• Introduce  $\phi$ -functions to make it work

| x ←                                                        | x <sub>0</sub> ←                      |

|------------------------------------------------------------|---------------------------------------|

| у ←                                                        | y₀ ←                                  |

| while $(x < k)$                                            | if $(x_0 \ge k)$ goto next            |

| $x \leftarrow x + 1$                                       | loop: $x_1 \leftarrow \phi(x_0, x_2)$ |

| $y \leftarrow y + x$                                       | $y_1 \leftarrow \phi(y_0, y_2)$       |

| Strengths of SSA-form                                      | $x_2 \leftarrow x_1 + 1$              |

|                                                            | $y_2 \leftarrow y_1 + x_2$            |

| <ul> <li>each use refers to a single definition</li> </ul> | nition if $(x_2 < k)$ goto loop       |

|                                                            |                                       |

SSA-form

•••

• (sometimes) faster algorithms next:

# Using Multiple Representations

- Repeatedly lower the level of the intermediate representation

- Each intermediate representation is suited towards certain optimizations

- Example: the Open64 compiler

- WHIRL intermediate format

- → Consists of 5 different IRs that are progressively more detailed and less abstract

# Memory Models

Two major models

- Register-to-register model

- Keep all values that can legally be stored in a register in registers

- Ignore machine limitations on number of registers

- Compiler back-end must insert loads and stores

use virtual registers!

- Memory-to-memory model

- Keep all values in memory

- Only promote values to registers directly before they are used

- Compiler back-end can remove loads and stores

- Compilers for RISC machines usually use register-to-register

Easier to determine when registers are used

The Rest of the Story...

Representing the code is only part of an IR

The compiler must discover and store many distinct kinds of information

For a variable it has to store its data type, storage class, the level of its declaring procedure, and a base and offset in memory

For an array also the number of dimension and the upper and lower bounds of each dimension

It often uses centralised information

- Symbol table

- Constant table

It needs an efficient and expandable way to realise them!

# Symbol Tables

Classic approach uses hashing because we need a constant-time expected lookup

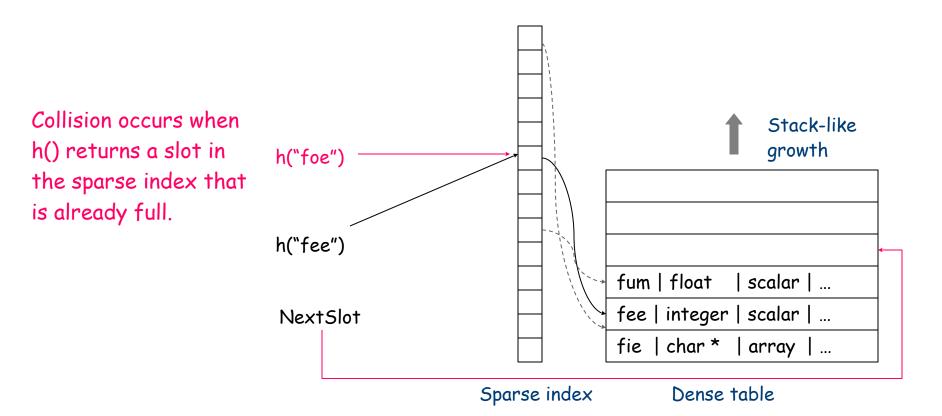

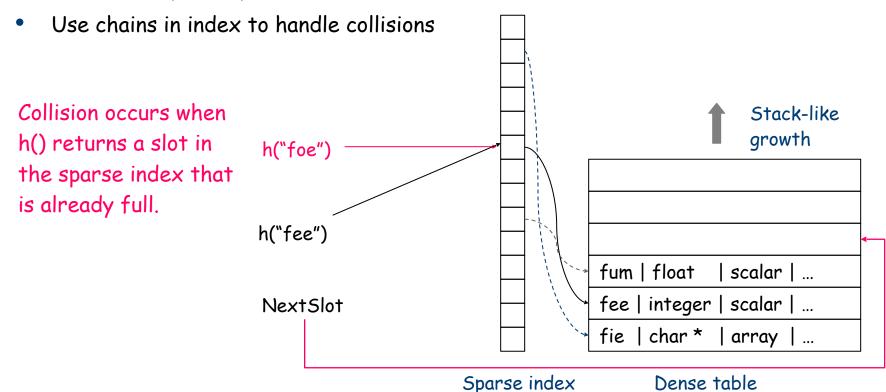

A two-table scheme

- Sparse index to reduce chance of collisions

- Dense table to hold actual data

→ Easy to expand, to traverse, to read & write from/to files

## Hash-less Symbol Tables

Classic approach to building a symbol table uses hashing

- Some concern about worst-case behavior

- Collisions in the hash function can lead to linear search

- Some authors advocate "perfect" hash for keyword lookup